ALI Aladdin IV+ (M1531)

Date: 2016-08-09

Tags: info vieilleries

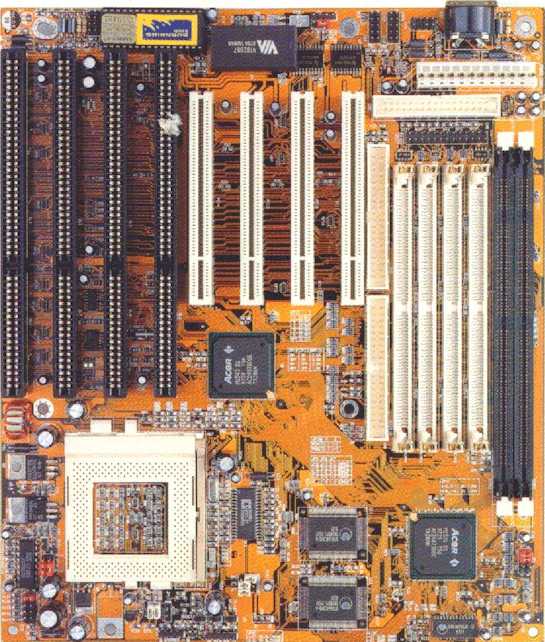

J’ai utilisé une carte mère PC-Chips M560, et j’ai découvert qu’elle fonctionnait correctement avec une seule barrette de mémoire SIMM (la seconde était mal enfoncée).

Cette carte-mère utilise un chipset Ali M1531 (maquillé en “TX-Pro”) pour supporter un processeur en socket 7 (Pentium/Pentium MMX, Cyrix 6x86/MII, AMD K5/K6, …), de la mémoire SIMM (FPM/EDO) et DIMM (EDO/SDRAM en 3.3V et 5V) et un bus PCI.

Tout le reste est géré par une puce Ali M1543 (hub PCI, ISA, IDE, Power Management, gestion d’interruptions/I/O), ça permet d’éviter d’utiliser une autre puce pour gérer les I/O.

Bus Mémoire

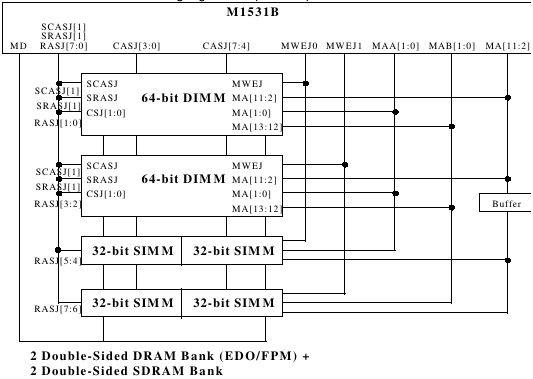

Normalement, les processeurs compatibles 586 ont un bus mémoire large de 64 bits. De ce fait, les banques mémoire font la même taille, et utilisent soit une barrette DIMM (64bits), soit deux barrettes SIMM (2×32bits).

Comme les barrettes de mémoire SIMM ont deux faces qui peuvent être identiques, il aurait été possible d’utiliser une barrette double face (2×32bits) dans une seule banque mémoire.

Bande passante théorique

En négligeant les temps de génération des adresses et de préchargement, ce qui est possible en mode “burst” (accès de plusieurs zones mémoires contigues) avec de la SDRAM, on obtient :

ce qui donne :

Seulement, la mémoire FPM n’est pas capable de gérer un mode “burst”, et il n’est pas toujours possible d’utiliser ce mode, même avec de la SDRAM.

En utilisant les temps d’accès, on peut avoir une mesure un peu plus réaliste, mais on ignore toujours la génération d’adresse, mais ça semble être “compensé” par la mémoire cache (sur de petites quantités de données).

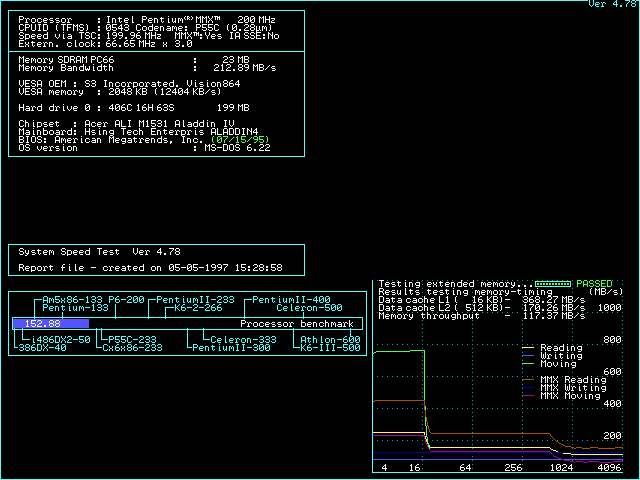

Protocole de test

La carte mère est utilisée avec un processeur Intel Pentium MMX à 200MHz (2.5×66MHz), le BIOS est réglé avec les mémoires cache L1 et L2 activées et les timings par défaut (70ns pour la SIMM FPM, 60ns pour la SIMM EDO, CAS 3 pour la SDRAM). Memtest est utilisé avec une passe rapide pour s’assurer qu’aucune barrette n’est pas défectueuse ou bien qu’il n’y a pas de faux contact.

Par la suite, Speedsys est utilisé pour mesurer la durée des opérations de lecture, écriture et déplacement sur 4Mio, au début de la zone mémoire.

Résultats de tests

Comme j’ai remarqué que la carte-mère fonctionnait avec une seule barrette de mémoire, j’ai testé plusieurs configurations en mesurant le débit de la mémoire.

- 1 barrette SIMM EDO simple face (82Mio/s)

- 2 barrettes SIMM EDO simple face (123Mio/s)

- 1 barrette SIMM EDO double face (82Mio/s)

- 1 barrette SIMM FPM double face (68Mio/s)

- 2 barrettes SIMM FPM double face (108Mio/s)

- 2 barrettes SIMM différentes, SIMM FPM double face + SIMM EDO simple face (69Mio/s)

- 1 barrette DIMM SDRAM (117Mio/s)

- 1 barrette SIMM + une barrette DIMM

- 2 barrettes SIMM + une barrette DIMM

- 1 barrette DIMM EDO buffered (fail)

En mesurant le débit, on remarque que le mode 32bits “single-SIMM” est 1/3 plus lent que le mode 64bits natif. On peut voir que les tests avec une seule barrette SIMM donnent les mêmes résultats indépendamment du nombre de faces des barrettes. On peut en déduire que chaque face est câblée sur une seule banque de mémoire.

Les tests avec de la mémoire DIMM et SIMM ne donnent que les performances de la mémoire DIMM, puisque le benchmark utilisé ne teste que 4Mio de la mémoire RAM.

On peut remarquer que la mémoire EDO (60ns) est plus rapide que la mémoire SDRAM dans ce cas-là (SDRAM 66MHz, CAS 3, soit 67.5ns).

En mode “single SIMM”, les débits pratiques sont 20% plus rapides qu’en théorie, ce qui suppose un bricolage ou une optimisation.

L’architecture mémoire est décrite dans la datasheet du chipset Ali 1531B, dans les sections 3.2 à 3.5, 3.9-3.10 et 5.2-5.3 et confirme que le fonctionnement avec une seule barrette SIMM 32bits est prévu.

Références

- Socket 7 Chipsets Datasheets

- Ali 1531B Aladdin IV Chipset Datasheet

- M560 Motherboard - mbarron, manuel PCCHIPS M560 rev 3.1

- Speedsys 4.78 benchmark

- ← Previous page

Sandisk Sansa Clip+ - Next page →

Alimentation 24V - boitier

Electronics Électronique puissance semiconducteur semiconductors power Hardware CPE INSA Xavier Bourgeois

RSS - Blog

RSS - Blog