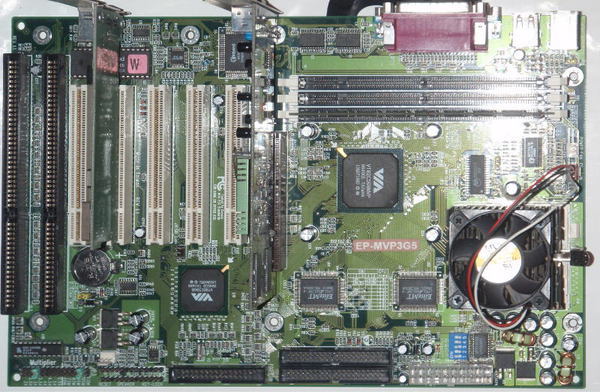

Carte-mère Epox EP-MVP3G5

Date: 2015-11-16

Tags: hardware info vieilleries

Présentation

- Socket : super 7 (Pentium - K6-2+/k6-3+, 321pins, 100~600MHz)

- Chipset/Northbridge : VIA MVP3 - VT82C598MVP (AGP, PCI, 3*128Mio SDRAM@100MHz)

- Chipset/Southbridge : VIA VT82C596B (PCI-PCI bridge, PCI-ISA bridge, RTC, 2 UDMA-33)

- Cache : EliteMT LP61C64128F-4 (2Mio, 4ns)

- I/O : Winbond W83877TF (Floppy, Parallel, 2 Serial)

- HW Monitor : W83781D (I²C/SMbus)

- PLL : Winbond W83194R-58A (66 - 150MHz CPU, SDRAM, 60~84MHz AGP, 30~45MHz PCI, 24/48MHz ISA/USB)

- EEPROM : Winbond W29C020C-90B (256kio, 8bits, 5V)

Alimentation

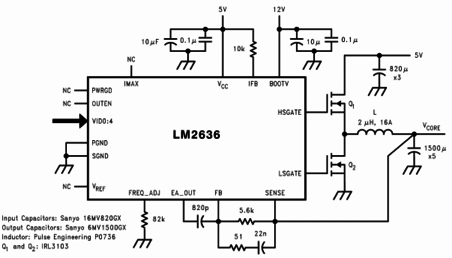

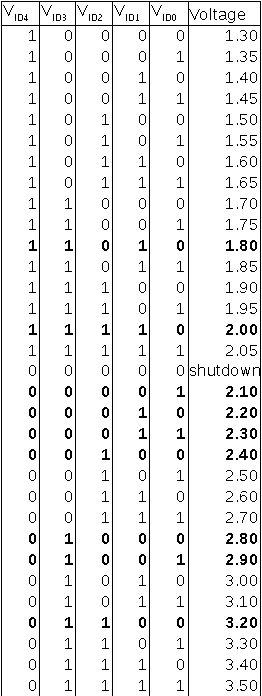

Le core du processeur est alimenté par une alimentation buck synchrone contrôlée en PWM par un LM2636, qui génère sa tension de référence avec un DAC réglable par des entrées numériques VID[0:4].

Les transistors MOSFET (STP-40NE03L20) sont prévus pour fournir au moins 30A. Il n’y a aucun marquage sur la self, mais elle devrait avoir un courant de saturation >15A.

Les processeurs compatibles avec cette carte sont alimentables entre 2V et 3.5V, seulement toutes les tension possibles ne sont pas affichées :

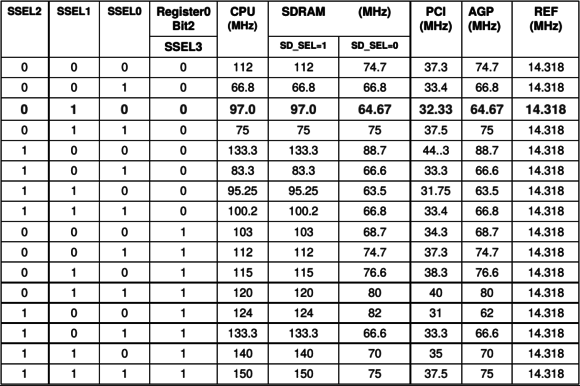

PLL

Les horloges de toute la carte sont générées par une PLL Winbond W83194R-58A. Les horloges “auxiliaires” doivent être le plus proches de leur fréquence nominale (peu d’intérêt a overclocker un clavier ou le bus USB). Le bus PCI peut poser des problèmes à plus de 40MHz (cartes réseau, contrôleur de disque dur). Le bus AGP pose peu de problèmes à >80MHz des AGP4x.

Le plus grand intérêt est d’augmenter la bande passante du bus mémoire et d’augmenter la fréquence du processeur.

Sur cette carte-mère, le PLL est configurable par des cavaliers (remappés par un GAL16V8). Seules 6 fréquences sont configurables par des cavaliers. Mais le PLL est aussi accessible par un bus I²C qui est câblé sur le southbridge.

On charge le driver du bus I²C, et on va scanner le bus :

# modprobe i2c-viapro

# i2cdetect -r 1

WARNING! This program can confuse your I2C bus, cause data loss and worse!

I will probe file /dev/i2c-1 using read byte commands.

I will probe address range 0x03-0x77.

Continue? [Y/n]

0 1 2 3 4 5 6 7 8 9 a b c d e f

00: -- -- -- -- -- -- -- -- -- -- -- -- --

10: -- -- -- -- -- -- -- -- -- -- -- -- -- -- -- --

20: -- -- -- -- -- -- -- -- -- -- -- -- -- -- -- --

30: -- -- -- -- -- -- -- -- -- -- -- -- -- -- -- --

40: -- -- -- -- -- -- -- -- -- -- -- -- -- -- -- --

50: 50 -- -- -- -- -- -- -- -- -- -- -- -- -- -- --

60: -- -- -- -- -- -- -- -- -- 69 -- -- -- -- -- --

70: -- -- -- -- -- -- -- -- Ici, l’adresse 0x50 correspond à l’EEPROM contenue sur les barrettes mémoire (SPD). Le PLL qui nous intéresse est situé à l’adresse 0x69.

# i2cdump 1 0x69 s

WARNING! This program can confuse your I2C bus, cause data loss and worse!

I will probe file /dev/i2c-1, address 0x69, mode smbus block

Continue? [Y/n]

0 1 2 3 4 5 6 7 8 9 a b c d e f 0123456789abcdef

00: 00 0f 71 0f c0 13 00 .?q???.Dans la datasheet du PLL, le registre 0x00 correspond au choix de la fréquence. Tant que le bit 3 est à 0, la fréquence est choisie matériellement.

Les fréquences sont utilisables avec les bits SSEL[0:3] (Registre 0x00, SSEL[0:2] sur les bits 4:6, SSEL3 sur le bit 2.

Faire fonctionner le CPU à une fréquence faible (multiplieur et FSB) permet de pouvoir tester chaque fréquence de bus sans risque d’avoir un système instable.

En écrivant 0x18 dans le registre 0x00, on règle la fréquence à 66MHz (aucun changement), mais on le règle via le bus I²C. # i2cset -y 1 0x69 0x00 0x18 s

En écrivant 0x38 dans le registre 0x00, on règle la fréquence à 75MHz. # i2cset -y 1 0x69 0x00 0x38 s Comme il n’y a aucun changement (le noyau ne surveille pas la fréquence du processeur), il faut tester la fréquence avec un benchmark dépendant de la fréquence du processeur (une boucle d’un grand nombre d’itération devrait être suffisante).

Par contre la machine se fige en tentant de passer de 66MHz à 83MHz ou 100MHz. Il est probable que certaines horloges doivent être stoppées avant de changer de prescaler pour rester dans leurs tolérances (du coup ce n’est pas vraiment gérable depuis un OS).

Références

- i2cdetect, i2cdump, i2cset, version >3.0, packages Debian i2c-tools ou lm-sensors : outils pour contrôler les bus I²C d’un PC.

- Epox EP-MPV3G5 - manuel de la carte mère

- LM2636 - datasheet, contrôleur PWM

- Winbond W83194R-58A - datasheet, PLL

- Exemple i2c-tools

- nbench - benchmark dépendant du CPU

- ← Previous page

RPL, PXE et carte réseau ISA - Next page →

D-Link DIR-615

Electronics Électronique puissance semiconducteur semiconductors power Hardware CPE INSA Xavier Bourgeois

RSS - Blog

RSS - Blog